# **NEPTUNE Single Board Computer**

EPIC Form-factor Embedded Computer with Integrated Data Acquisition and Configurable CPU

| Revision | Date      | Comment                          |

|----------|-----------|----------------------------------|

| 1.5      | 9/08/2009 | Initial release                  |

| 2.0      | 5/13/14   | New AMD G-Series models          |

| 2.1      | 5/15/15   | New Intel Bay Trail E3845 models |

|          |           |                                  |

FOR TECHNICAL SUPPORT PLEASE CONTACT:

support@diamondsystems.com

Copyright © 2015

Diamond Systems Corp.

555 Ellis Street

Mountain View, CA 94043 USA

Tel 1-650-810-2500

Fax 1-650-810-2525

www.diamondsystems.com

# **CONTENTS**

| Important Safe-Handling Information                                            | 5  |

|--------------------------------------------------------------------------------|----|

| 1. Introduction                                                                |    |

| 1.1 Key Features                                                               | 7  |

| 1.1.1 ETX Computer-on-Module (COM) Features                                    | 7  |

| 1.1.2 Neptune Baseboard Features                                               |    |

| 1.2 Software Compatibility                                                     | 8  |

| 1.3 Thermal Considerations and Heatspreader                                    | 9  |

| 1.4 Panel I/O Board Option                                                     | 9  |

| 2. Functional Overview                                                         | 10 |

| 2.1 Block Diagrams                                                             | 10 |

| 2.2 Board Diagrams                                                             |    |

| 2.3 Interface Connector Summary                                                | 14 |

| 2.4 Configuration Jumper Summary                                               | 15 |

| 3. Getting Started                                                             |    |

| 3.1 Introducing the Neptune Development Kit                                    |    |

| 3.1.1 Neptune Cable Kit                                                        |    |

| 3.1.2 Neptune Panel I/O Board                                                  |    |

| 3.1.3 512MB Flashdisk with Linux                                               |    |

| 3.1.4 Flashdisk Programmer Board                                               |    |

| 3.1.5 AC Adapter                                                               |    |

| 3.1.6 Miscellaneous Cables                                                     |    |

| 3.1.7 Software and Documentation CD                                            |    |

| 3.2 System Setup                                                               |    |

| 3.2.1 Installing the Flashdisk                                                 |    |

| 3.2.2 Installing the Neptune Panel I/O Board                                   |    |

| 3.2.3 Connecting display, keyboard, and mouse peripherals                      |    |

| 3.2.4 Connecting Power                                                         |    |

| 3.3 Booting the System                                                         |    |

| 3.4 Demonstrating Data Acquisition Operation                                   |    |

| 3.5.1 BIOS Setup                                                               |    |

| 3.5.2 Operating System Drivers                                                 |    |

| 3.5.3 Using a Hard Drive, CD-ROM, or other IDE device along with the FlashDisk |    |

| 3.5.4 Installing the Flashdisk Programmer Board                                |    |

| 4. Interface Connector Details                                                 |    |

| 4.1 PC/104- <i>Plus</i> stacking location (J1, J2, J3)                         |    |

| 4.1.1 PC/104- <i>Plus</i> ISA Bus (J1, J2)                                     |    |

| 4.1.2 PC/104- <i>Plus</i> PCI Bus (J3)                                         |    |

| 4.2 ETX Utility (J4)                                                           |    |

| 4.3 Variable Input Power (J5)                                                  |    |

| 4.4 Panel I/O Board Input Power (J6)                                           |    |

| 4.5 Keyboard and Mouse Ports (J7)                                              |    |

| 4.6 VGA Display (J8)                                                           |    |

| 4.7 USB 2.0 (J10)                                                              |    |

| 4.8 CompactFlash (J12)                                                         |    |

| 4.9 IDE (J13, J14)                                                             | 36 |

| 4.10 LCD LVDS Interface (J16)                                                  | 37 |

| 4.11 LCD LVDS Control (J17)                                                    | 38 |

| 4.12 Audio (J18)                                                               | 39 |

| 4.13 Utility (J22)                                                             | 40 |

| 4.13.1 ATX Power Button Considerations                                         |    |

| 4.14 HDD Power (J23)                                                           |    |

| 4.15 ETX Ethernet (J24)                                                        |    |

| 4.16 Analog I/O (J30)                                                          |    |

| 4.17 Digital I/O (J31)                                                         |    |

| 4.18 Optoisolated I/O (J33)                                                    |    |

| 4.19 COM1-COM4 (J34)                                                           |    |

| 4.19.1 RS-232 Pin Assignment                                                   |    |

| 4.19.2 RS-485 Pin Assignment                                                   |    |

| 4.19.3 RS-422 Pin Assianment                                                   | 40 |

|    | 4 00       | 0014 | F COME (127)                                     | F^  |

|----|------------|------|--------------------------------------------------|-----|

|    |            |      | 5-COM6 (J37)                                     |     |

|    |            |      | bit LED Connector (J39)                          |     |

|    |            |      | style Input Power (J44)                          |     |

|    |            |      | ATX-style Input Power Considerations             |     |

|    |            |      | bit Ethernet (T1)                                |     |

|    |            |      | A (SATA1, SATA2)                                 |     |

|    |            |      | (LPC1)                                           |     |

|    |            |      | DDI1)                                            |     |

| 5. | Co         |      | ration Jumper Details                            |     |

|    | 5.1        |      | I I/O TTL/RS-232 Selection (J11)                 |     |

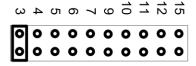

|    |            |      | /IRQ/Address/Bus Configuration (J26)             |     |

|    | 5.2        |      | DMA Level Configuration                          | 56  |

|    | 5.2        |      | IRQ Level Configuration                          |     |

|    | 5.2        |      | Base Address Selection                           |     |

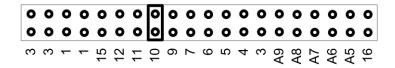

|    | 5.2        |      | Bus Width Selection                              |     |

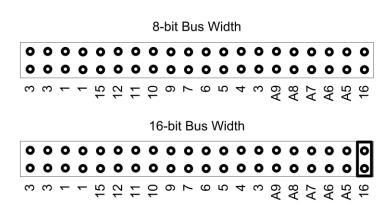

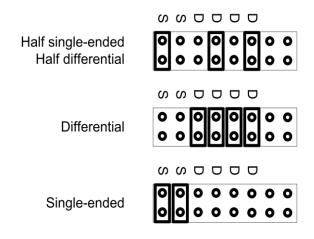

|    | 5.3        |      | e-ended/Differential Selection (J28)             |     |

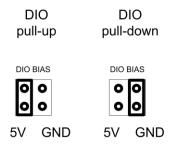

|    | 5.4        |      | Pull-up/Pull-down Selection (J32)                |     |

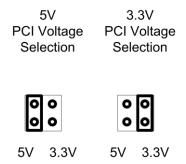

|    | 5.5        |      | /oltage Selection (J35)                          |     |

|    | 5.6        |      | Selection (J38)                                  |     |

|    | 5.7        |      | 1-COM4 / CF Configuration (J40)                  |     |

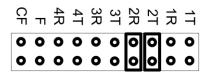

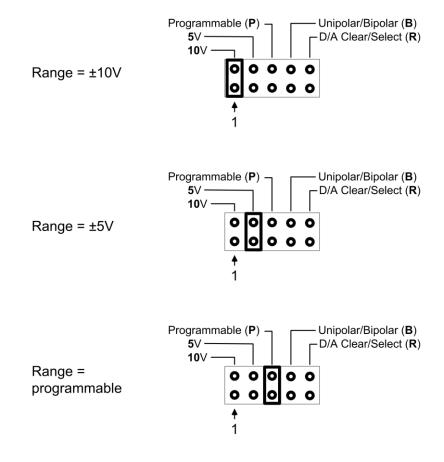

|    | 5.8        |      | Configuration (J43)                              |     |

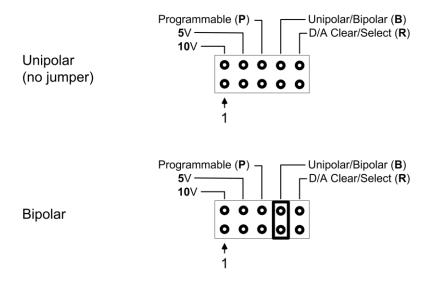

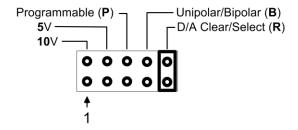

|    | 5.8        |      | D/A Range                                        |     |

|    | 5.8        |      | D/A Polarity                                     |     |

|    | 5.8        |      | D/A Clear Select                                 |     |

| 6. |            |      | Baseboard I/O Register Map                       |     |

|    |            | •    | view                                             |     |

|    |            |      | une Baseboard I/O Register Summary               |     |

|    |            |      | Write Register Definitions                       |     |

|    | 6.2        |      | Read Register Definitions                        |     |

|    | 6.3        |      | une Baseboard I/O Register Description           |     |

|    |            |      | s 0–11                                           |     |

|    | 6.3        |      | Page 0 Register Definitions                      |     |

|    | 6.3        |      | Page 1 Register Definitions                      |     |

|    | 6.3        |      | Page 2 Register Definitions                      |     |

|    | 6.3        |      | Page 3 Register Definitions                      |     |

|    | 6.3        |      | Page 5 Register Definitions                      |     |

|    | 6.3        |      | Registers 16-23                                  |     |

| 7  |            |      | I/O Operation                                    |     |

|    |            | _    | nput Ranges and Resolution                       |     |

|    |            |      | plar and Bipolar Inputs                          |     |

|    | 7.3        |      | es and Resolutions                               |     |

|    | 7.3<br>7.3 | _    | Conversion Formulas                              |     |

|    |            |      | Sampling Methods                                 |     |

|    | 7.4<br>7.4 |      | 1 0                                              |     |

|    | 7.4<br>7.4 |      | Sampling Modes                                   |     |

|    |            |      | FIFO Description                                 |     |

|    | 7.4        |      | Scan Sampling                                    |     |

|    | 7.4        |      | Sequential Sampling                              |     |

|    |            |      | Conversion                                       |     |

|    | 7.5        |      | Select the Input Channel                         |     |

|    | 7.5        |      | Select the Input Range                           |     |

|    | 7.5        |      | Wait for Analog Input Circuit to Settle          |     |

|    | 7.5        |      | Perform an A/D Conversion on the Current Channel |     |

|    | 7.5        |      | Wait for the Conversion to Finish                |     |

|    | 7.5        |      | Read the Data from the Board                     |     |

|    | 7.5        |      | Convert the numerical data to a meaningful value |     |

|    | 7.5        |      | A/D Conversion Using Interrupts                  |     |

|    |            |      | Conversion                                       |     |

|    | 7.6        |      | Resolution                                       |     |

|    | 7.6        |      | Full-scale Range Selection                       |     |

|    | 7.6        |      | Performing a D/A Conversion                      |     |

|    | 7.7        |      | eform Generator1                                 |     |

|    | 7.7        | ' 1  | Programming the D/A Waveform Generator           | 109 |

|                                                 | •   |

|-------------------------------------------------|-----|

| 7.7.2 Enable Enhanced Features                  | 109 |

| 7.7.3 Reset D/A Waveform Pointer                |     |

| 7.7.4 Latch D/A Value                           |     |

| 7.7.5 Store D/A Values into Buffer              | 109 |

| 7.7.6 Setup D/A Waveform Settings               | 109 |

| 7.7.7 Start D/A Waveform Generator              | 110 |

| 7.8 Auto-calibration                            | 110 |

| 7.8.1 Background                                | 110 |

| 7.8.2 Performing Auto-calibration with Software | 111 |

| 8. Digital I/O Operation                        | 111 |

| 8.1 Main Digital I/O Internal 82C55 Circuit     | 111 |

| 8.1.1 Mode 0 Digital I/O                        |     |

| 8.1.2 Mode 1 Digital I/O With Handshaking       | 112 |

| 8.2 Auxiliary Digital I/O                       | 112 |

| 8.2.1 Outputs                                   | 112 |

| 8.2.2 Inputs                                    | 113 |

| 8.3 Optoisolated I/O                            | 113 |

| 8.3.1 Opto output                               | 113 |

| 8.3.2 Opto input                                | 113 |

| 9. Counter/Timer Operation                      |     |

| 9.1.1 Features and Configuration Options        |     |

| 9.1.2 Counter/Timer Configuration               | 114 |

| 9.1.3 Counter/Timer Access and Programming      | 115 |

| 10. Watchdog Timer Operation                    | 115 |

| 11. EEPROM Operation                            | 115 |

| 11.1 EEPROM Map and Description                 | 115 |

| 11.2 How to Use the EEPROM                      | 116 |

| 11.2.1 EPROM Write Operation                    | 116 |

| 11.2.2 EEPROM Read Operation                    | 116 |

| 11.2.3 EEPROM Reload Operation                  | 116 |

| 12. Data Acquisition Subsystem Specifications   |     |

| 12.1 Analog Inputs                              | 117 |

| 12.2 Analog Outputs                             | 117 |

| 12.3 Programmable Digital I/O Port              | 117 |

| 12.4 Optoisolated Inputs and Outputs            |     |

| 12.5 Counter/Timers                             | 117 |

| 13 Mating Connector Reference                   | 112 |

#### IMPORTANT SAFE-HANDLING INFORMATION

- WARNING!

- ESD-Sensitive Electronic Equipment.

- Observe ESD-safe handling procedures when working with this product.

- Always use this product in a properly grounded work area and wear appropriate ESD-preventive clothing and/or accessories.

- Always store this product in ESD-protective packaging when not in use.

### Safe Handling Precautions

Neptune contains numerous I/O connectors that connect to sensitive electronic components. This creates many opportunities for accidental damage during handling, installation and connection to other equipment. The list here describes common causes of failure found on boards returned to Diamond Systems for repair. This information is provided as a source of advice to help you prevent damaging your Diamond (or any vendor's) embedded computer boards.

**ESD damage** — This type of damage is almost impossible to detect, because there is no visual sign of failure or damage. The symptom is that the board simply stops working because some component becomes defective. Usually the failure can be identified and the chip can be replaced.

To prevent ESD damage, always follow proper ESD-prevention practices when handling computer boards.

**Damage during handling or storage** — On some boards, we have noticed physical damage from mishandling. A common observation is that a screwdriver slipped while installing the board, causing a gouge in the PCB surface and cutting signal traces or damaging components.

Another common observation is damaged board corners, indicating the board was dropped. This may or may not cause damage to the circuitry, depending on what is near the corner. Most of our boards are designed with at least 25 mils clearance between the board edge and any component pad, and ground / power planes are at least 20 mils from the edge to avoid possible shorting from this type of damage. However, these design rules are not sufficient to prevent damage in all situations.

A third cause of failure is when a metal screwdriver tip slips, or a screw drops onto the board while it is powered on, causing a short between a power pin and a signal pin on a component. This can cause overvoltage / power supply problems described below. To avoid this type of failure, only perform assembly operations when the system is powered off.

Sometimes boards are stored in racks with slots that grip the edge of the board. This is a common practice for board manufacturers. However, our boards are generally very dense, and if the board has components very close to the board edge, they can be damaged or even knocked off the board when the board tilts back in the rack. Diamond recommends that all our boards be stored only in individual ESD-safe packaging. If multiple boards are stored together, they should be contained in bins with dividers between boards. Do not pile boards on top of each other or cram too many boards into a small location. This can cause damage to connector pins or fragile components.

**Power supply wired backwards** — Our power supplies and boards are not designed to withstand a reverse power supply connection. This will destroy each IC that is connected to the power supply. In this case the board will most likely will be unrepairable and must be replaced. A chip destroyed by reverse power or by excessive power will often have a visible hole on the top or show some deformation on the top surface due to vaporization inside the package. **Check twice before applying power!**

**Board not installed properly in PC/104 stack** — A common error is to install a PC/104 board accidentally shifted by 1 row or 1 column. If the board is installed incorrectly, it is possible for power and ground signals on the bus to make contact with the wrong pins on the board, which can damage the board. For example, this can damage components attached to the data bus, because it puts the  $\pm 12V$  power supply lines directly on data bus lines.

Overvoltage on analog input — If a voltage applied to an analog input exceeds the design specification of the board, the input multiplexor and/or parts behind it can be damaged. Most of our boards will withstand an erroneous connection of up to  $\pm 35$ V on the analog inputs, even when the board is powered off, but not all boards, and not in all conditions.

Overvoltage on analog output — If an analog output is accidentally connected to another output signal or a power supply voltage, the output can be damaged. On most of our boards, a short circuit to ground on an analog output will not cause trouble.

Overvoltage on digital I/O line — The digital circuitry can be damaged if a digital I/O signal is connected to a voltage above the Neptune's maximum specified voltage. On most of our boards the acceptable range of voltages connected to digital I/O signals is 0-5V, and they can withstand about 0.5V beyond that (-0.5 to 5.5V) before being damaged. However logic signals at 12V and even 24V are common, and if one of these is connected to a 5V logic chip, the chip will be damaged, and the damage could even extend past that chip to others in the circuit.

**Bent connector pins** — This type of problem is often only a cosmetic issue and is easily fixed by bending the pins back to their proper shape one at a time with needle-nose pliers. The most common cause of bent connector pins is when a PC/104 board is pulled off the stack by rocking it back and forth left to right, from one end of the connector to the other. As the board is rocked back and forth it pulls out suddenly, and the pins at the end get bent significantly. The same situation can occur when pulling a ribbon cable off of a pin header. If the pins are bent too severely, bending them back can cause them to weaken unacceptably or even break, and the connector must be replaced.

#### 1. INTRODUCTION

Neptune introduces a new concept in small form-factor, board-level embedded computing.

Neptune's core embedded-PC functionality is implemented with an ETX CPU module mounted on the bottom side of an I/O baseboard. This approach results in several benefits including enhanced thermal management, increased space for I/O functions and interface connectors, and scalable processing power. Accordingly, Neptune integrates the equivalent functions of up to six embedded boards — CPU, system I/O, industry-leading data acquisition, gigabit Ethernet, and a wide-input DC-to-DC power supply — all within the compact and modularly-expandable EPIC single board computer form-factor.

Thanks to Neptune's modular architecture, you can select from a wide range of ETX-based CPUs to meet each application's specific performance, power, and cost requirements. Available processors include two of the AMD Fusion G-Series CPUs, the T56N and T40N. What's more, Neptune's on-board PC/104-*Plus* stack location facilitates the addition of both custom and off-the-shelf ISA- and PCI-interfaced expansion modules, to tune system functionality to the application's precise requirements.

Neptune is offered in a range of models that vary according to the choice of ETX CPU Module, on-board SO-DIMM SDRAM capacity, +5V input or variable-input DC/DC supply, and choice of operating temperature.

#### 1.1 Key Features

Neptune's extensive set of features derives from functions present on the Neptune baseboard plus additional functions provided by the attached ETX computer-on-module (COM) macrocomponent. Both are summarized below.

#### 1.1.1 ETX Computer-on-Module (COM) Features

- Processor: Choice of Intel Bay Trail E3845 CPU, AMD Fusion G-Series G-T56N or G-T40N CPUs

- RAM: 200-pin SO-DIMM socket; supports up to 8GB DDR3 SDRAM

- Graphics:

- VGA CRT interface

- LCD flat panel interface (LVDS); provides LCD backlight control signals

- SDVO interface (connector directly on ETX COM, when available)

- Audio: AC'97 CODEC; mic in, line in/out signals

- 1 IDE interface; support two devices (Master/Slave) in PIO or UDMA mode

- 2 SATA ports, supporting one device each (interface connectors directly on ETX COM)

- Ethernet interface: 1 10/100Mbps port (magnetic provided on baseboard)

- 2 serial ports, supporting TTL or RS-232 signaling (signal buffers and mode selection provided on baseboard)

- Keyboard/mouse: PS/2; USB keyboard/mouse also supported

- USB: 4 USB 2.0 ports

- Other: SMbus, IrDA serial interfaces; PC speaker output; watchdog timer

- Dual system expansion buses: 16-bit ISA and 32-bit PCI

- ETX 3.0 compliant form-factor (physical and electrical)

**Note:** The ETX COM features listed below are typical. Refer to the appropriate ETX CPU module's user manual for detailed specifications.

#### 1.1.2 Neptune Baseboard Features

- Additional Ethernet interface: 10/100/1000Base-T port with RJ-45 connector

- 4 additional serial ports:

- 2 RS-232/422/485

- 2 TTL/RS-232

- Industry-leading data acquisition subsystem:

- 32 16-bit A/D inputs usable as: 32 single-ended / 16 differential / 16 SE + 8 DI

- 4 12-bit D/A channels

- 2 programmable counter/timers

- 24 programmable bidirectional digital I/O lines with 5V logic

- 8 optoisolated digital inputs and outputs

- EEPROM configuration data storage for instant availability on power-up

- Status LEDs:

- Power LED

- Ethernet link and speed LEDs

- ATX-style power input and control

- On-board RTC backup battery and connector for external battery

- ETX COM socket on bottom; conforms to ETX v3.0 specification

- I/O connectors provided for all I/O

- Solid State Disk:

- On-board CompactFlash I/II socket

- Mounting position for optional IDE FlashDisk

- On-board PC/104-Plus socket; supports ISA and PCI expansion buses

- Optional Built-in DC/DC power supply:

- Input voltage: +5V or +8V to +28V DC

- Power consumption: 2.5W, without ETX module

- Output power: maximum 45W, total

- Output voltages: +5V, +3.3V (on PCI bus)

- Switched outputs: +5V, +12V, +3.3V

- Operating temperature: up to -40°C to +85°C (depends on ETX COM)

- Operating humidity: 5% to 95% non-condensing

- Form-factor:

- 4.53 x 6.50 inches (115mm x 165mm)

- EPIC SBC dimensions and mounting holes

### 1.2 Software Compatibility

Neptune's operating system compatibility depends on both the Neptune baseboard and the specific ETX CPU module attached to it. The baseboard has been qualified for use with the following operating systems:

- Windows XP, Windows XP Embedded SP2

- Linux v2.6.23

The operating systems supported by the ETX CPU module vary according to the specific ETX module used. Consult the appropriate ETX CPU module's user manual for details on its OS (operating system) support.

#### 1.3 Thermal Considerations and Heatspreader

All models of Neptune are specified for an operating temperature range of either -20°C to +71°C or -40°C to +85°C depending on which ETX CPU module is selected. Diamond Systems provides a heatspreader attached to Neptune as a conductive cooled thermal layer. However, this heatspreader by itself does not constitute the complete thermal solution necessary for any specific implementation, but provides a common interface between the single board computer and the customer's implementation-specific thermal solution.

The outside surface of the Neptune heatspreader must be kept at a temperature not to exceed +71°C or +85°C, again depending on the COM module. If your environment causes the temperature on the outside surface of the heatspreader to exceed the appropriate temperature, you are responsible for removing the additional heat from the system through either an additional passive thermal solution or fan solution.

Neptune's integrated heatspreader makes thermal contact with the heat generating components and provides a flat surface on the bottom of the assembly for mating to the system enclosure. This technique facilitates efficient removal of heat from the COM module without the need for a fan. Four mounting holes on the bottom of the conduction cooled heatspreader are provided to mount Neptune in an enclosure or to a bulkhead. These mounting holes are #6-32 threaded holes on 2.8" centers.

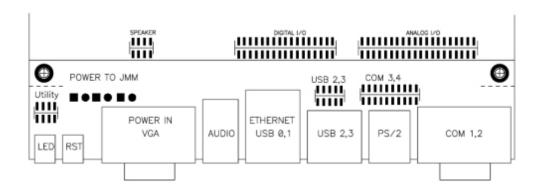

#### 1.4 Panel I/O Board Option

The ETX module's I/O signals are available on header connectors along the edges of the Neptune baseboard. A Panel I/O Board is available that plugs into the Neptune baseboard and routes these to standard PC-style peripheral interface connectors.

#### 2. FUNCTIONAL OVERVIEW

### 2.1 Block Diagrams

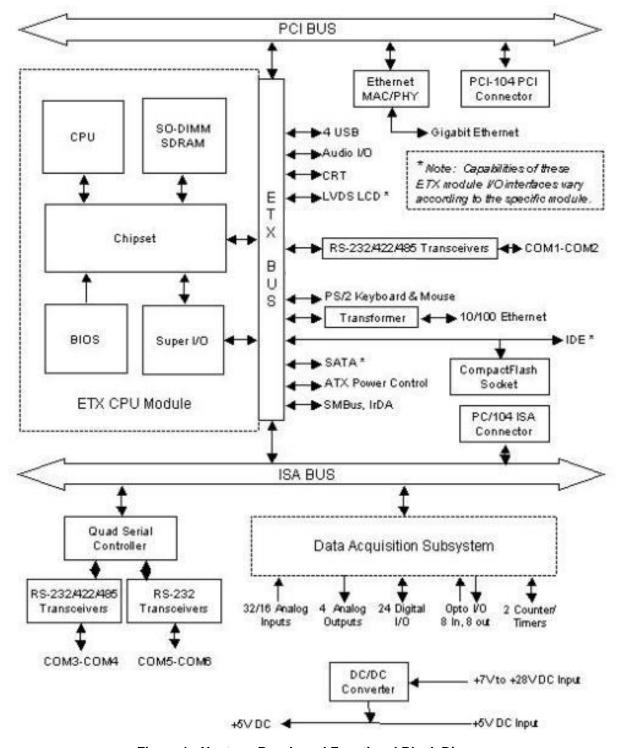

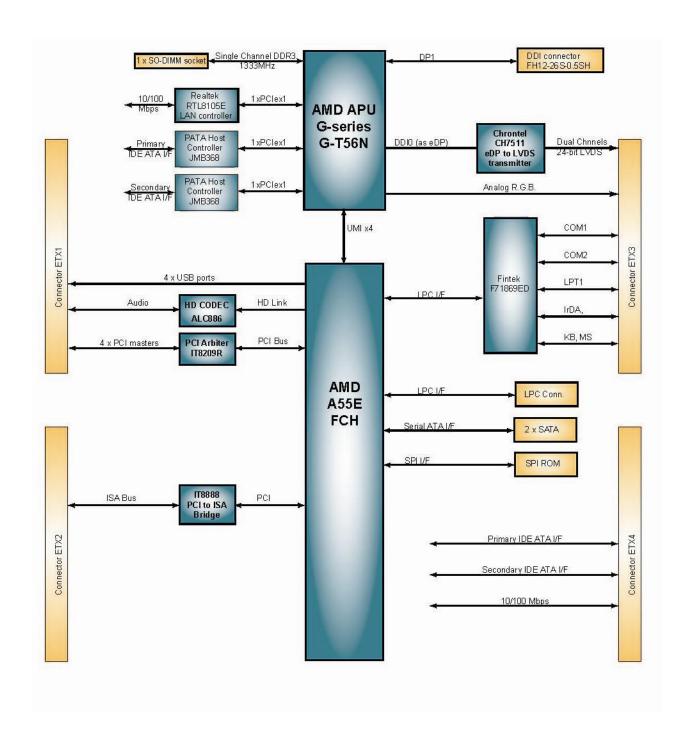

Figure 1 shows Neptune's functional blocks, including circuitry contained on both the Neptune baseboard and the ETX CPU module. As indicated in the block diagram, the baseboard circuitry primarily comprises the data acquisition subsystem, gigabit Ethernet controller, DC/DC power supply, and I/O interfaces, while the ETX module integrates the system's core embedded PC functionality. Although ETX CPU module processors and precise functions vary between specific modules, the block diagram of a typical ETX CPU module is shown in Figure 2.

Figure 1: Neptune Baseboard Functional Block Diagram

Figure 2: Typical ETX CPU Module Functional Block Diagram

### 2.2 Board Diagrams

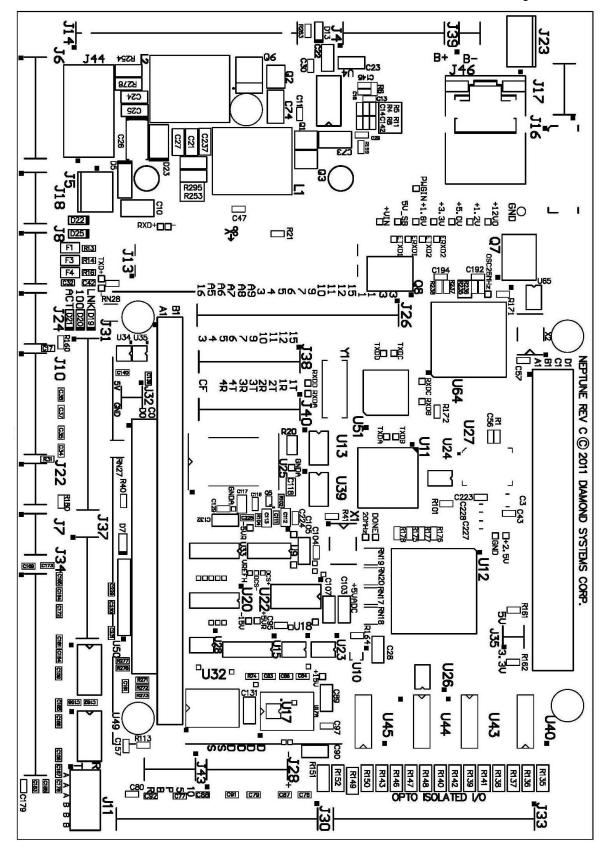

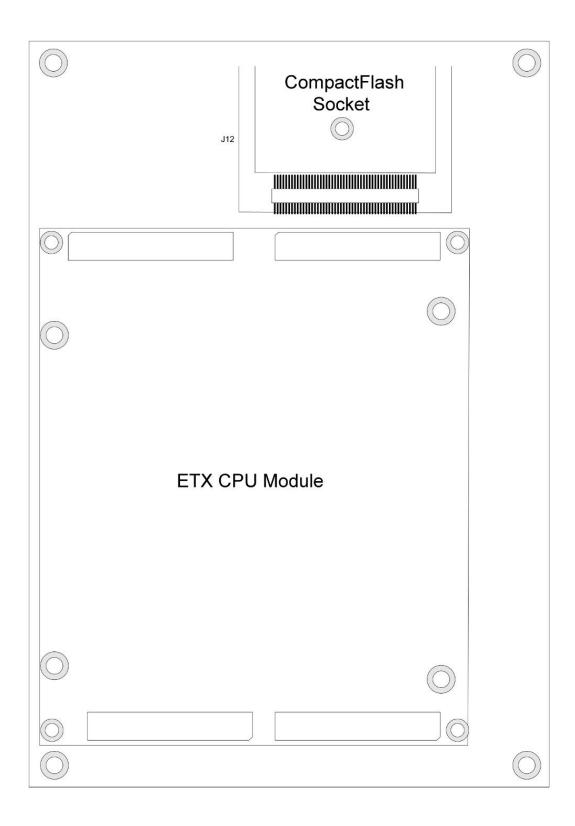

Figures 3 and 4 illustrate the location of connectors and jumpers on the top and bottom side of the Neptune baseboard. The ETX CPU module attaches on the baseboard's bottom side, as indicated in Figure 3.

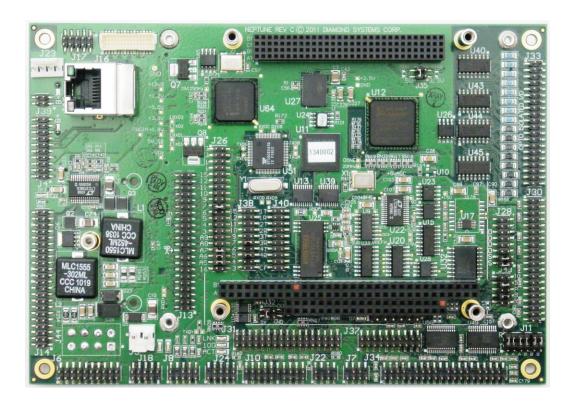

Figure 3: Neptune Top View

Figure 4: Neptune Bottom View

### 2.3 Interface Connector Summary

The table below summarizes the functions of Neptune's interface, utility, and power connectors. The table also identifies which major subsystem — ETX CPU module or Neptune baseboard — provides the electronics associated with each connector.

The table indicates which connectors mate with the optional Neptune Panel I/O Board (discussed elsewhere in this section), which provides standard PC-style I/O connectors. Alternatively, Diamond offers an optional Neptune Cable Kit (discussed in Section 5), which provides mating cable assemblies for most of Neptune's I/O interface connectors.

Signal functions relating to all of Neptune's interfaces connectors are discussed in greater detail in Section 6.

| Interface Function          | Connector<br>Designation | Associated<br>Subsystem | Supported by Panel I/O Board? | Supported by Cable Kit? |

|-----------------------------|--------------------------|-------------------------|-------------------------------|-------------------------|

| PC/104-Plus ISA Bus         | J1, J2                   | ETX CPU module          | n/a                           | n/a                     |

| PC/104-Plus PCI Bus         | J3                       | ETX CPU module          | n/a                           | n/a                     |

| ETX Utility                 | J4                       | ETX CPU module          | No                            | Yes                     |

| Variable Input Power        | J5                       | Neptune baseboard       | No                            | Yes                     |

| Panel I/O Board Input Power | J6                       | Neptune baseboard       | No                            | No                      |

| Keyboard and Mouse Ports    | J7                       | ETX CPU module          | Yes                           | Yes                     |

| VGA Display                 | J8                       | ETX CPU module          | Yes                           | Yes                     |

| USB 2.0                     | J10                      | ETX CPU module          | Yes                           | Yes                     |

| CompactFlash                | J12                      | ETX CPU module          | No                            | n/a                     |

| IDE (Primary)               | J13, J14                 | ETX CPU module          | No                            | Yes                     |

| LCD LVDS Interface          | J16                      | ETX CPU module          | No                            | No                      |

| LCD LVDS Control            | J17                      | Neptune baseboard       | No                            | No                      |

| Audio                       | J18                      | ETX CPU module          | Yes                           | Yes                     |

| Utility                     | J22                      | Neptune baseboard       | No                            | Yes                     |

| HDD Power                   | J23                      | Neptune baseboard       | No                            | Yes                     |

| ETX Ethernet                | J24                      | ETX CPU module          | Yes                           | Yes                     |

| Analog I/O                  | J30                      | Neptune baseboard       | No                            | Yes                     |

| Digital I/O                 | J31                      | Neptune baseboard       | No                            | Yes                     |

| Optoisolated I/O            | J33                      | Neptune baseboard       | No                            | Yes                     |

| COM1-COM4                   | J34                      | Neptune baseboard       | No                            | Yes                     |

| COM5-COM6                   | J37                      | ETX CPU module          | Yes                           | Yes                     |

| Gigabit LED Connector       | J39                      | Neptune baseboard       | No                            | No                      |

| ATX-style Input Power       | J44                      | Neptune baseboard       | No                            | Yes                     |

| Gigabit Ethernet            | T1                       | Neptune baseboard       | No                            | No                      |

| SATA interfaces             | SATA1, SATA2             | ETX CPU module          | No                            | No                      |

| Serial Digital Video Output | SDVO                     | ETX CPU module          | No                            | No                      |

**Note:** ETX COM I/O functions vary according to the specific ETX module that is attached to the Neptune baseboard. For further details on functions listed above that are generated by the ETX CPU module, consult the specific ETX CPU module's user manual. SATA1/SATA2 and SDVO, when available, are supported by connectors directly on the ETX module.

# 2.4 Configuration Jumper Summary

The Neptune baseboard's configuration jumper blocks are listed below. Details regarding the use of these jumpers appear in Section 5 of this document.

| Jumper | Description                           |

|--------|---------------------------------------|

| J11    | Serial I/O TTL/RS-232 Selection       |

| J26    | DMA / IRQ / Address Bus Configuration |

| J28    | Single-ended / Differential Selection |

| J32    | DIO Pull-up/Pull-down Selection       |

| J35    | PCI Voltage selection                 |

| J38    | IRQ Selection                         |

| J40    | COM1-4 / CF Configuration             |

| J43    | DAC Configuration                     |

#### 3. GETTING STARTED

First-time Neptune users normally receive the product as part of Diamond's Neptune Development Kit, which provides everything needed to ensure rapid application development. This section of the Neptune User Manual covers basic hardware setup, power connection, system boot-up, and initial software configuration. After Neptune is up and running, refer to the later sections of this manual for the detailed hardware and software reference information needed to adapt the product to specific applications.

This section begins with a simple series of quick-start steps for rapidly bringing up Neptune and verifying its proper operation. The steps provided assume the use of Diamond's Neptune Development Kit.

The Neptune quick-start process basically consists of the following steps:

- Install the Diamond IDE FlashDisk Drive with bootable Linux binary on the primary IDE connector.

- 2. Install the Neptune Panel I/O Board on its mating connectors.

- 3. Connect a VGA monitor.

- 4. Connect PS/2- or USB-based keyboard and mouse peripherals.

- 5. Connect the Neptune AC Adapter to the Neptune baseboard's power connector.

- 6. Turn on the monitor and plug in the AC Adapter.

- 7. At this point, Neptune should boot-up to a Linux prompt.

The above steps will be discussed in detail, after the brief overview of the Neptune Development Kit and its contents that follows.

#### Important Safe-Handling Information

WARNING: ESD-Sensitive Electronic Equipment!

Observe ESD-safe handling procedures when working with this product.

Always use this product in a properly grounded work area and wear appropriate ESD-preventive clothing and/or accessories.

Always store this product in ESD-protective packaging when not in use.

Please refer to page 5 of this manual ("Important Safe-Handling Information") for further details.

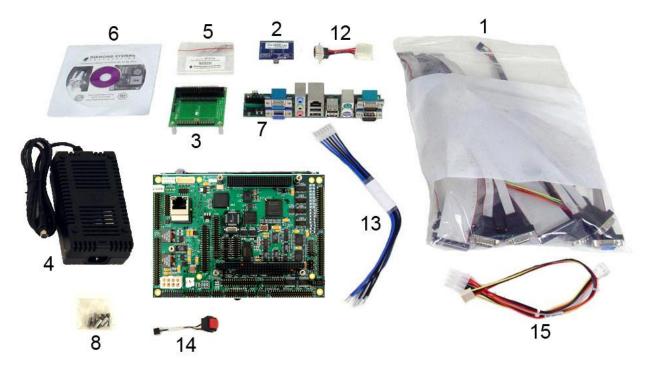

# 3.1 Introducing the Neptune Development Kit

The Neptune Development Kit provides everything required for Neptune-based rapid application development. The photos and table below identify the boards, cables, and other items included in the kit.

The fifteen Neptune Development Kit items pictured above are identified below.

| Item | Diamond P/N  | Description                                                                               |

|------|--------------|-------------------------------------------------------------------------------------------|

| 1    | C-NPT-KIT    | Neptune Cable Kit                                                                         |

| 2    | DK-LNX-NPT   | 512MB FlashDisk with bootable Linux, CD                                                   |

| 3    | ACC-IDEEXT   | FlashDisk Programmer Board (includes 40- and 44-pin IDE cables)                           |

| 4    | PS-5V-04     | AC Adapter (100-240VAC in, 5VDC @ 8A out)                                                 |

| 5    | 6810041      | Neptune Panel I/O Board mounting hardware (not shown)                                     |

| 6    | 6710010      | Neptune software and documentation CD                                                     |

| 7    | PNL-NPT-01   | Neptune Panel I/O Board                                                                   |

| 8    | MTG104       | PC/104 Mounting Hardware                                                                  |

| 9    | NPT-xxxx-xxx | Neptune SBC (model number varies according to which Development Kit was ordered)          |

| 12   | 6981093      | Transition cable for power interface between AC Adapter and Panel I/O Board               |

| 13   | 6981092      | Cable for power interface between Panel I/O Board and optional PC/104 power supply module |

| 14   | 6981094      | Power button interface to Panel I/O Board Utility connector                               |

| 15   | 6981006      | Auxiliary power interface for 40-pin IDE devices (CD-ROM)                                 |

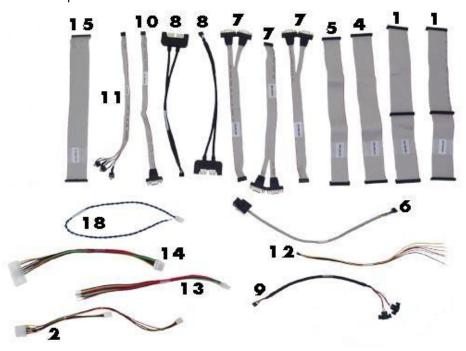

#### 3.1.1 Neptune Cable Kit

The Neptune cable kit (part number C-NPT-KIT) provides convenient access to all of Neptune's I/O features. The kit's cables are shown in the photo below and are identified in the table that follows.

The components of the Neptune Cable Kit are listed below.

| 1       2       6981004       IDE (44-pin)       J13, 14         2       1       6981006       Power output         4       1       6981072       Analog I/O       J30         5       1       6981073       Digital I/O       J31         6       1       6981080       100Mbit Ethernet       J24         7       3       6981081       Dual serial       J34, J37         8       2       6981082       Dual USB       J10         9       1       6981083       Keyboard/Mouse       J7         10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5         14       1       6981091       ATX-style input power       J44 | Item | Qty | Diamond P/N | Description               | Connects to |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------------|---------------------------|-------------|

| 4       1       6981072       Analog I/O       J30         5       1       6981073       Digital I/O       J31         6       1       6981080       100Mbit Ethernet       J24         7       3       6981081       Dual serial       J34, J37         8       2       6981082       Dual USB       J10         9       1       6981083       Keyboard/Mouse       J7         10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                            | 1    | 2   | 6981004     | IDE (44-pin)              | J13, 14     |

| 5       1       6981073       Digital I/O       J31         6       1       6981080       100Mbit Ethernet       J24         7       3       6981081       Dual serial       J34, J37         8       2       6981082       Dual USB       J10         9       1       6981083       Keyboard/Mouse       J7         10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                                                                                       | 2    | 1   | 6981006     | Power output              |             |

| 6       1       6981080       100Mbit Ethernet       J24         7       3       6981081       Dual serial       J34, J37         8       2       6981082       Dual USB       J10         9       1       6981083       Keyboard/Mouse       J7         10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                                                                                                                                                   | 4    | 1   | 6981072     | Analog I/O                | J30         |

| 7       3       6981081       Dual serial       J34, J37         8       2       6981082       Dual USB       J10         9       1       6981083       Keyboard/Mouse       J7         10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                                                                                                                                                                                                                    | 5    | 1   | 6981073     | Digital I/O               | J31         |

| 8       2       6981082       Dual USB       J10         9       1       6981083       Keyboard/Mouse       J7         10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6    | 1   | 6981080     | 100Mbit Ethernet          | J24         |

| 9       1       6981083       Keyboard/Mouse       J7         10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7    | 3   | 6981081     | Dual serial               | J34, J37    |

| 10       1       6981084       VGA out       J8         11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8    | 2   | 6981082     | Dual USB                  | J10         |

| 11       1       6981085       Audio I/O       J18         12       1       6981088       Baseboard utility signals       J4         13       1       6981090       Power input cable       J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9    | 1   | 6981083     | Keyboard/Mouse            | J7          |

| 12 1 6981088 Baseboard utility signals J4  13 1 6981090 Power input cable J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10   | 1   | 6981084     | VGA out                   | J8          |

| 13 1 6981090 Power input cable J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11   | 1   | 6981085     | Audio I/O                 | J18         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12   | 1   | 6981088     | Baseboard utility signals | J4          |

| 14 1 6981091 ATX-style input power J44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13   | 1   | 6981090     | Power input cable         | J5          |

| -2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14   | 1   | 6981091     | ATX-style input power     | J44         |

| 15 1 6981141 Optically isolated I/O J33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15   | 1   | 6981141     | Optically isolated I/O    | J33         |

| 18 1 6981144 Variable DC input power J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18   | 1   | 6981144     | Variable DC input power   | J5          |

#### 3.1.2 Neptune Panel I/O Board

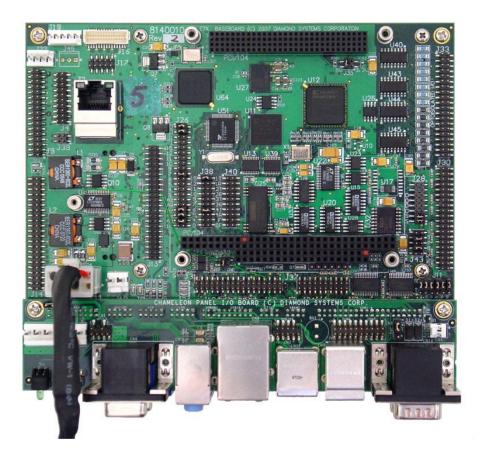

The Neptune Panel I/O Board mates with the bank of connectors located along the side of the Neptune baseboard, as shown in the figures below. The board provides standard connector access for many of Neptune's PC-style interfaces, a reset button, and a power LED.

Neptune Panel I/O Board, Front and Top views

#### 3.1.3 512MB Flashdisk with Linux

The Neptune Development Kit contains a 512MB IDE solid-state flashdisk preformatted with Diamond's compact, quick-boot Linux OS based on a 2.6.x kernel. The Linux system utilizes the Minix file system for enhanced file protection during power loss or improper shutdown, and Grub bootloader for boot-up. In addition to the Linux OS, the flashdisk image includes Diamond's Universal Driver, which supports the Neptune baseboard's data acquisition functions.

A binary image of contents of the flashdisk device is also included in the Neptune Software Development Kit. This image may be used for preparing additional Neptune-based systems for operation. A Neptune Linux Software Development Kit (SDK), which includes OS source code along with a complete development toolchain, is also available (contact Diamond for further details).

#### 3.1.4 Flashdisk Programmer Board

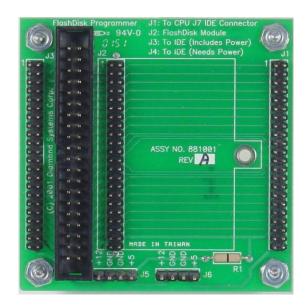

The flashdisk Programmer Board allows a flashdisk and an external IDE drive to share the Neptune baseboard's primary IDE connector (J13). In this case, the flashdisk and external device are used as Master and Slave IDE devices, respectively. The flashdisk Programmer Board provides the flexibility of interfacing to external drives requiring either 40- or 44-pin IDE cables.

The flashdisk Programmer Board is not required on Neptune configurations with ETX CPU modules that provide a secondary IDE channel; in this case, an external IDE device can be connected to the baseboard's secondary IDE connector (J14). In addition, on Neptune assemblies whose ETX CPU module has built-in SATA connector(s), a SATA-interfaced drive can be used in lieu of an IDE drive attached to a flashdisk Programmer Board.

#### 3.1.5 AC Adapter

An AC Adapter (P/N PS-5V-04), included in the Neptune Development Kit, converts a 110VAC to 240VAC power source to 5VDC suitable for powering a Neptune SBC. The AC Adapter's power output cable is equipped with a connector that mates with the Neptune baseboard's ATX-style input power connector (J44).

**Note:** There are numerous ways to power a Neptune-based system — according to the power source and its voltage, whether the application requires instant-on access or use of a power switch (or button), and whether ATX-style soft shutdown is required.

#### 3.1.6 Miscellaneous Cables

Three additional special-function cables are included in the Neptune Development Kit:

- 6981092 Used when the Panel I/O Board is present along with a wide-voltage PC/104 Power Supply module, such as Diamond's Jupiter MM. This routes incoming power from the Panel I/O Board to the PC/104 Power Supply module. This cable is included in Panel I/O Board Kit.

- 6981093 Connects between the AC Adapter (PS-5V-04) and the DB9 power input connector on the Panel I/O Board. Allows the use of the AC Adapter when Neptune and a Panel I/O Board are mounted within an enclosure such as Diamond's Triton. This cable is included in Panel I/O Board Kit.

- 6981006 Provides power from the Neptune board to an IDE device having a 40-pin interface.

#### 3.1.7 Software and Documentation CD

The Neptune Development Kit also includes a Software and Documentation CD, which contains Neptune documentation (including this manual) and support software. The CD provides drivers specific to the Neptune baseboard and its attached ETX CPU module, for operation under Windows XP, Windows XP Embedded, and Linux. The CD also contains Diamond's Universal Driver Software, which supports the analog and digital I/O capabilities of the Neptune baseboard, including binaries and full documentation.

#### 3.2 System Setup

#### 3.2.1 Installing the Flashdisk

The flashdisk module installs directly on the Neptune baseboard's primary IDE connector (J13) and attaches via a spacer and two screws to a mounting hole on the baseboard. Mounting hardware is provided in the Neptune Development Kit in the packet marked with DSC# 6801008. Use the following installation procedure:

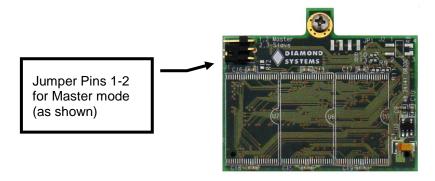

1. To ensure that Neptune boots directly from the flashdisk, place the jumper block over pins 1–2. This configures the flashdisk as an IDE Master device. See the figure below.

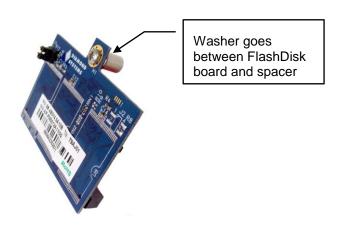

- 2. Connect round spacer DSC# 6841002 to the flashdisk module using one 2-56x pan head screw and one #2 flat washer. The spacer should be on the side of the flashdisk module with the female IDE connector. The washer should be on the top of the spacer. See the figure below.

- 3. Attach the female IDE connector on the flashdisk to the IDE connector J13 on the Neptune board.

- 4. Fasten the flashdisk in place by inserting one 2-56x pan head screw from the solder side of the Neptune board into the round spacer.

The figure below shows the Neptune baseboard with the flashdisk attached.

#### 3.2.2 Installing the Neptune Panel I/O Board

Install the Neptune Panel I/O Board on the Neptune baseboard as follows, using the Panel I/O Board Mounting Hardware Kit (part number 6810041) provided in the Neptune Development Kit:

- 1. Carefully mate the Panel I/O Board with the set of eight 2 mm pin-header connectors located on the edge of the Neptune board, as shown in the figures below.

- 2. Screw a pan head Phillips 4-40 screw through each of the two mounting holes from the top (component side) of the Panel I/O Board into the 7 mm round spacer provided on the top of the Neptune board.

#### 3.2.3 Connecting display, keyboard, and mouse peripherals

Neptune provides both VGA monitor and LVDS flat panel display interfaces. Recognizing the complexities associated with connection to parallel-interfaced flat panels, this quick-start process assumes the use of a standard VGA-compatible monitor (LCD or CRT). Connect a VGA-compatible display to the female DB15 connector on the Panel I/O Board.

The Neptune SBC supports either PS/2- or USB-based keyboard and mouse devices. Connect these devices to the corresponding connectors on the Panel I/O Board.

**Note:** a mouse is not required for basic operation of the Neptune-based system when booting from the flashdisk's quick-boot Linux OS.

#### 3.2.4 Connecting Power

Connect the power output cable from the AC Adapter (P/N PS-5V-04) to its mating connector (J44) on the Neptune baseboard. At this point — with the flashdisk, Panel I/O Board, and AC Adapter installed as described above — your Neptune setup should appear as shown below.

Neptune with Panel I/O Board and power cable installed

### 3.3 Booting the System

Plug in and turn on the VGA video display. Then, attach the power cord to the PS-5V-04 AC Adapter, and plug the power cord into an AC power outlet.

Neptune should power up immediately, displaying information regarding the BIOS and Diamond Linux followed by a system prompt.

#### 3.4 Demonstrating Data Acquisition Operation

The Linux installed on the flashdisk contains software demonstration programs for Neptune's data acquisition features. You may access the directory of these programs by typing:

#### >cd /home/NEPTUNE

The source code, makefile, and executables of the demonstration programs reside in this directory. Each demonstration program executable (and its source code) appears in its own directory. A good first demonstration program to run is the DSCADAutoCal program.

The DSCADAutocal program will calibrate the Neptune baseboard's A/D data acquisition circuitry to guarantee accurate A/D input readings. To run the program type the following while in the demonstration programs directory:

#### >./DSCADAutoCal/DSCADAutoCal

The program will ask you to input the following values:

- Base address: This is the base address of the board determined by jumper settings on J26, see page 55 for more details. For demonstration purposes type 0x300.

- Range to calibrate: This is the A/D modes users would typically calibrate. The modes are 0-3, 8-15. For demonstration purposes type 255.

- Range to boot: This is the A/D mode users typically boot up the board in. The modes are 0-3, 8-15. For demonstration purposes type 0.

Once initiated, the program will calibrate the mode the user specified. The process may take up to 15 seconds, after which the error values will be printed on screen for each mode; values less than +-2 are within tolerance.

For more details regarding A/D modes refer to section "Input Ranges and Resolutions" in the data acquisition sections of this document. For more information regarding the data acquisition software API and functions please refer to the Diamond Systems Universal Driver software manual <u>located here</u>.

#### 3.5 Additional System Configuration

### 3.5.1 BIOS Setup

The Neptune ETX CPU module's BIOS ROM provides a wide range of configuration options. When you power up Neptune, you can immediately enter the BIOS "Setup" utility (prior to OS boot-up) in order to adjust BIOS settings to match your system's peripheral devices and other requirements, and to configure various other hardware and software parameters.

Options configurable via Setup typically include:

- Number and type of mass storage devices

- · Boot device priority

- Video display type and resolution

- IDE, serial, and parallel interface modes and protocols

- PCI and PnP configuration

- Power management setup

- Automatic power-up after LAN connection, RTC alarm, power resumption, etc.

- System monitoring and security functions

The precise configuration options available via the BIOS Setup utility — and the specific keystroke sequence required to launch Setup on power-up — vary according to the specific ETX CPU module attached to the Neptune Baseboard. Refer to the ETX CPU module's user manual for further details.

#### 3.5.2 Operating System Drivers

Depending on the operating system to be installed on your Neptune setup, it may be necessary to install software drivers for on-board interface controllers. The driver requirements (if any) will depend on both the Neptune Baseboard and the attached ETX CPU module. Drivers for Windows XP and Linux 2.6, if required, are included on the Software and Documentation CD that is included in the Neptune Development Kit. This software is also available for download from Diamond's website.

#### 3.5.3 Using a Hard Drive, CD-ROM, or other IDE device along with the FlashDisk

There are several ways to attach additional devices such as hard drives and CD-ROM drives to the Neptune system, while continuing to use the provided flashdisk as a primary boot device:

- Attach a second IDE device to the primary IDE interface using the flashdisk Programmer Board to provide a simultaneous connection of both the flashdisk module and the IDE device. Instructions are provided below regarding installation and use of the flashdisk Programmer Board.

- 2. In Neptune configurations with an ETX CPU module that includes one or two SATA interfaces, you can connect a SATA hard drive directly to a SATA connector on the ETX module using a standard internal SATA cable (generally available with the drive).

#### 3.5.4 Installing the Flashdisk Programmer Board

The flashdisk Programmer Board (FDPB) provided with the Neptune Development Kit enables the simultaneous connection of both a flashdisk module and a standard IDE hard drive or CD-ROM drive to the primary IDE connector on the Neptune board.

- 1. Install the flashdisk to the Flashdisk Programmer Board using the instructions provided earlier in this chapter.

- 2. Attach the female IDE connector on the flashdisk to the IDE connector (J2) on the FDPB.

- 3. Fasten the flashdisk in place by inserting one 2-56x pan head screw from the solder side of the FDPB board into the round spacer. The figure below shows the appearance of the Neptune board with the flashdisk attached.

- 4. Connect the connector J1 on the FDPB to the primary IDE connector (J13) on the Neptune baseboard using one of the 44-wire ribbon-cables (DSC# 6981004) from the Neptune Cable Kit.

- 5. Connect the IDE device to either the 40-pin (0.1-inch spacing) J4 connector on the FDPB or the 44-pin (2 mm spacing) J3 connector on the FDPB. Any two devices (i.e. flashdisk and HDD) may be connected simultaneously using this board with proper master / slave jumper configurations on the devices. Since the flashdisk is configured as an IDE Master, be sure to configure the added IDE device as a Slave.

**Note:** The 44-pin connectors (J1, J2, and J3) and mating cables carry +5V power, but the 40-pin connector (J4) and mating cable do not. J5 and J6 on the FDPB or J13 on the Neptune may be used to provide power to an IDE device when the device is attached to the 40-pin J4 connector on the FDPB using the Auxiliary Power Cable (DSC# 6981006) provided with the Neptune Development Kit. If +12V power is required, it must be supplied externally.

FlashDisk Programmer Board

#### 4. INTERFACE CONNECTOR DETAILS

This section describes functions associated with the Neptune baseboard's PC/104-*Plus* bus expansion stack, utility, and power interface connectors in greater detail. Refer to Section 3 of this document for information regarding mating cable assemblies that are provided in the Neptune cable and Panel I/O Board kits.

#### 4.1 PC/104-Plus stacking location (J1, J2, J3)

This set of three connectors accommodates the addition of either PC/104 (ISA bus only), PC/104-Plus (ISA and PCI buses), or PCI-104 (PCI bus only) modules on top of the Neptune baseboard. Specifications and other details on all three of these expansion module standards are available from the website of the PC/104 Consortium (<a href="http://www.pc104.org">http://www.pc104.org</a>).

#### 4.1.1 PC/104-Plus ISA Bus (J1, J2)

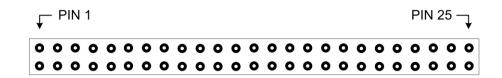

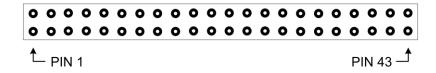

Connectors J1 (A/B) and J2 (C/D) carry the PC/104-*Plus* expansion stack location's 104-pin ISA bus signals. These signals, generated by Neptune's ETX CPU module, are essentially identical in function and signaling to those of the 16-bit PC/AT bus, except for the physical design.

A 64-pin header (J1) incorporates the 8-bit "PC bus" connector signals, while a 40-pin header (J2) incorporates the 16-bit bus connector signals. Additional grounds and keys (missing pins) have been added within the 104-pin PC/104-*Plus* ISA bus array comprised by J1 and J2.

The signal names and functions for J1 and J2 are listed in the table on the following page. The pin numbering represents the view from the top of the board.

#### J1 Connector

#### IOCHCHK-**A1 B1 GND A2** SD7 **B2 RESETDRV** SD6 А3 В3 +5V **A4** SD5 **B4** IRQ9 **A5** SD4 **B5** -5V SD3 **A6 B6** DRQ2 Α7 В7 -12V SD2 SD1 **A8 B8** ENDXFR-SD0 **A9 B9** +12V **IOCHRDY** A10 B10 Key (no pin) AEN A11 B11 SMEMW-SA19 A12 B12 SMEMR-SA18 A13 B13 IOW-SA17 A14 IOR-B14 SA16 A15 B15 DACK3-SA15 A16 B16 DRQ3 **SA14** A17 **B17** DACK1-**SA13** A18 **B18** DRQ1 SA12 A19 **B19** REFRESH-SA11 A20 **B20** SYSCLK SA10 **A21 B21** IRQ7 SA9 A22 **B22** IRQ6 SA8 A23 **B23** IRQ5 SA7 A24 **B24** IRQ4 SA6 A25 **B25** IRQ3 SA5 **A26 B26** DACK2-SA4 **A27 B27** TC SA3 A28 **B28 BALE** SA2 A29 **B29** +5V SA1 A30 **B30** OSC SA0 A31 **B31 GND** GND A32 **B32 GND**

#### J2 Connector

| GND          | CO        | D0  | GND     |

|--------------|-----------|-----|---------|

| SBHE-        | C1        | D1  | MEMCS16 |

| LA23         | C2        | D2  | IOCS16- |

| LA22         | C3        | D3  | IRQ10   |

| LA21         | C4        | D4  | IRQ11   |

| LA20         | C5        | D5  | IRQ12   |

| LA19         | C6        | D6  | IRQ15   |

| LA18         | <b>C7</b> | D7  | IRQ14   |

| LA17         | C8        | D8  | DACK0-  |

| MEMR-        | C9        | D9  | DRQ0    |

| MEMW-        | C10       | D10 | DACK5-  |

| SD8          | C11       | D11 | DRQ5    |

| SD9          | C12       | D12 | DACK6-  |

| SD10         | C13       | D13 | DRQ6    |

| SD11         | C14       | D14 | DACK7-  |

| SD12         | C15       | D15 | DRQ7    |

| SD13         | C16       | D16 | +5      |

| SD14         | C17       | D17 | MASTER- |

| SD15         | C18       | D18 | GND     |

| Key (no pin) | C19       | D19 | GND     |

|              |           |     |         |

#### 4.1.2 PC/104-Plus PCI Bus (J3)

The Neptune baseboard's PC/104-*Plus* PCI expansion bus signals are generated by the ETX CPU module, and are essentially identical in function and signaling to a normal PC motherboard's 32-bit PCI bus except for the physical connector, a 120-pin header (J3) arranged as four 30-pin rows. Several additional pins on the PC/104-*Plus* connectors implement added grounds and keys.

| GND/5.0V | A1  | B1  | Reserved | +5V      | C1  | D1  | AD00           |

|----------|-----|-----|----------|----------|-----|-----|----------------|

| VI/O     | A2  | B2  | AD02     | AD01     | C2  | D2  | +5V            |

| AD05     | А3  | В3  | GND      | AD04     | C3  | D3  | AD03           |

| CMD/BE0- | A4  | B4  | AD07     | GND      | C4  | D4  | AD06           |

| GND      | A5  | B5  | AD09     | AD08     | C5  | D5  | GND            |

| AD11     | A6  | B6  | VI/O     | AD10     | C6  | D6  | M66EN          |

| AD14     | A7  | B7  | AD13     | GND      | C7  | D7  | AD12           |

| +3.3V    | A8  | B8  | CMD/BE1- | AD15     | C8  | D8  | +3.3V          |

| SERR-    | A9  | B9  | GND      | SB0-     | C9  | D9  | PAR            |

| GND      | A10 | B10 | PERR-    | +3.3V    | C10 | D10 | SDONE          |

| STOP-    | A11 | B11 | +3.3V    | LOCK-    | C11 | D11 | GND            |

| +3.3V    | A12 | B12 | TRDY-    | GND      | C12 | D12 | DEVSEL-        |

| FRAME-   | A13 | B13 | GND      | IRDY-    | C13 | D13 | +3.3V          |

| GND      | A14 | B14 | AD16     | +3.3V    | C14 | D14 | CMD/BE2-       |

| AD18     | A15 | B15 | +3.3V    | AD17     | C15 | D15 | GND            |

| AD21     | A16 | B16 | AD20     | GND      | C16 | D16 | AD19           |

| +3.3V    | A17 | B17 | AD23     | AD22     | C17 | D17 | +3.3V          |

| IDSEL0   | A18 | B18 | GND      | IDSEL1   | C18 | D18 | IDSEL2         |

| AD24     | A19 | B19 | CMD/BE3  | VI/O     | C19 | D19 | IDSEL3         |

| GND      | A20 | B20 | AD26     | AD25     | C20 | D20 | GND            |

| AD29     | A21 | B21 | +5V      | AD28     | C21 | D21 | AD27           |

| +5V      | A22 | B22 | AD30     | GND      | C22 | D22 | AD31           |

| REQ0-    | A23 | B23 | GND      | REQ1-    | C23 | D23 | VI/O           |

| GND      | A24 | B24 | REQ2-    | +5V      | C24 | D24 | GNT0-          |

| GNT1-    | A25 | B25 | VI/O     | GNT2-    | C25 | D25 | GND            |

| +5V      | A26 | B26 | CLK0     | GND      | C26 | D26 | CLK1           |

| CLK2     | A27 | B27 | +5V      | CLK3     | C27 | D27 | GND            |

| GND      | A28 | B28 | INTD-    | +5V      | C28 | D28 | RST-           |

| +12V     | A29 | B29 | INTA-    | INTB-    | C29 | D29 | INTC-          |

| -12V     | A30 | B30 | Reserved | Reserved | C30 | D30 | GND / 3.3V KEY |

# 4.2 ETX Utility (J4)

The Neptune baseboard provides a 20-pin header with access to the ETX Utility signals listed in the table below.

**Note:** The signals on this connector's pins are defined by the ETX CPU module. Please refer to the particular ETX module's user manual for further details on the definition and utilization of these signals.

| BATT       | 1  | 2  | GND        |

|------------|----|----|------------|

| SMB_BTLOW- | 3  | 4  | SMB_DATA   |

| SMB_CLK    | 5  | 6  | I2_DAT     |

| I2_CLK     | 7  | 8  | JILI_DAT   |

| JILI_CLK   | 9  | 10 | GND        |

| IRDA_TX    | 11 | 12 | IRDA_RX    |

| RSM_RST-   | 13 | 14 | SMB_ALRT-  |

| SMB_GPE1-  | 15 | 16 | SMB_GPE2-  |

| EXT_SMI-   | 17 | 18 | (not used) |

| KB_INH     | 19 | 20 | (not used) |

|            |    |    |            |

| Signal     | Definition                                                                    |

|------------|-------------------------------------------------------------------------------|

| BATT       | 3V battery input for real-time clock and non-volatile memory                  |

| SMB_BTLOW- | Battery low input; drive low to signal low battery condition or other event   |

| SMB_CLK    | System bus management clock; e.g., support for temperature/battery monitoring |

| SMB_GPE1-  | General-purpose power management input event                                  |

| SMB_DATA   | System bus management data; e.g., support for temperature/battery monitoring  |

| SMB_ALRT-  | System management bus alert input; drive low to signal event on SMB           |

| SMB_GPE2-  | General-purpose power management input event                                  |

| I2_CLK     | No connection                                                                 |

| I2_DAT     | No connection                                                                 |

| IRDA_RX    | Infrared receive                                                              |

| IRDA_TX    | Infrared transmit                                                             |

| RSM_RST-   | Resume reset input; used to reset ETX module power management.                |

| JILI_CLK   | LCD panel parameter EEPROM I <sup>2</sup> C clock                             |

| JILI_DAT   | LCD panel parameter EEPROM I <sup>2</sup> C data                              |

| EXT_SMI-   | System management interrupt input; drive low to initiate interrupt event      |

| KB_INH     | Keyboard inhibit; assert to inhibit keyboard input                            |

| GND        | Ground                                                                        |

### 4.3 Variable Input Power (J5)

This connector is used for connection of an external +8V to +28V DC power source. Maximum DC/DC conversion efficiency will be achieved when this voltage is close to 28V DC.

| Signal | Definition                  |

|--------|-----------------------------|

| +VWIN  | +8 to +28V DC Input voltage |

| GND    | Ground                      |

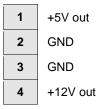

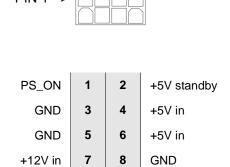

### 4.4 Panel I/O Board Input Power (J6)

This connector provides power input from a connector located on the Neptune I/O Panel. This provides a means to power Neptune through the I/O Panel when it is packaged within an enclosure.

| +5V in      | 1  | 2  | +5V in  |

|-------------|----|----|---------|

| +5V in      | 3  | 4  | +5V in  |

| +5V in      | 5  | 6  | +5V in  |

| +VWIN       | 7  | 8  | +VWIN   |

| GND         | 9  | 10 | GND     |

| GND         | 11 | 12 | GND     |

| GND         | 13 | 14 | GND     |

| GND         | 15 | 16 | GND     |

| +12V in     | 17 | 18 | +12V in |

| +5V standby | 19 | 20 | PS_ON   |

|             |    |    |         |

| Signal      | Definition                                                                                                      |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| +5V in      | +5V input                                                                                                       |

| +12V in     | +12V input                                                                                                      |

| +5V standby | +5V standby power; powers board when in standby mode.                                                           |

| PS_ON       | Power Supply ON. Feedback pin for external ATX supply, when needed; pulled low when on-board power is inactive. |

| +VWIN       | Variable input DC power: +5 to +28 VDC                                                                          |

| GND         | Ground                                                                                                          |

**Note:** Optionally, a power supply module plugged into Neptune's PC/104-Plus expansion stack location may be used to power the system through the power pins on the expansion module stacking bus.

# 4.5 Keyboard and Mouse Ports (J7)

Connector J7 provides signals for connection of PS/2-interfaced keyboard and mouse peripherals. This connector also mates with Neptune's optional Panel I/O Board, resulting in its signals being routed to standard PC-style connectors.

**Note:** The signals on this connector's pins are defined by the ETX CPU module. Please refer to the particular ETX module's user manual for further details on the definition and utilization of these signals.

| +5V out        | 1 | 2 | (not used)  |

|----------------|---|---|-------------|

| Keyboard data  | 3 | 4 | Mouse data  |

| Keyboard clock | 5 | 6 | Mouse clock |

| GND            | 7 | 8 | (not used)  |

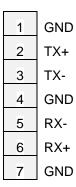

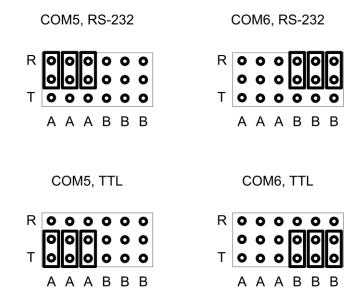

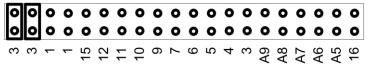

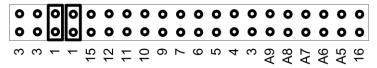

| Signal         | Definition                                                             |